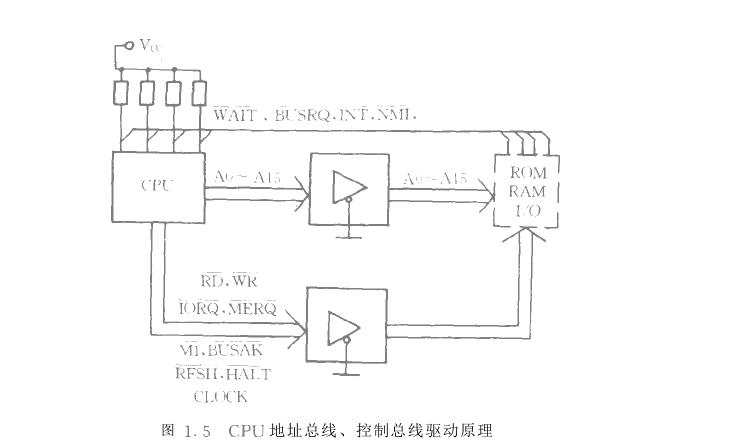

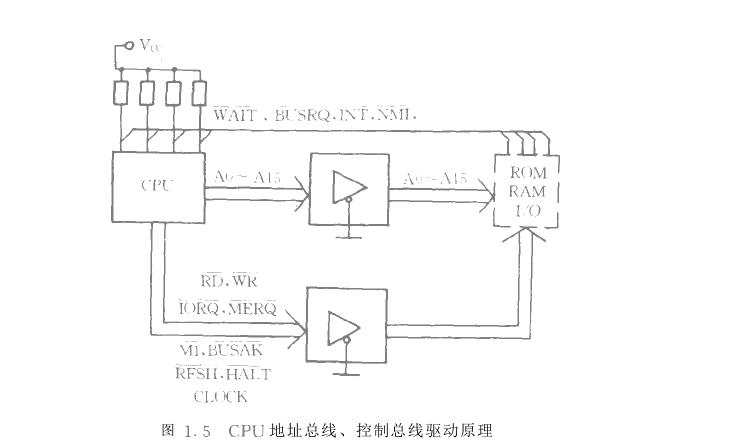

眾所周知,微處理器是通過總線(數據總線、地址總線、控制總線)與存儲器小接口交換數據、傳遞命令和各種信息的。通常CPD和單片機的總線驅動能力十分有限,大多不允許超過四個標準TTL外部擴展的芯片越多,微處理器負載越重,輕則引起芯片發熱,重則產生邏輯混亂,波形失真。因此凡結構比較復雜的微機系統,都必須強化總線的驅動能力按照信息流動的方向,總線有單向與雙向之分。地址總線及大部分控制總線、狀態線是單向的,可以通過恒定接通的單向總線緩沖器加以驅動。圖1.5所示的是CPU擴展地址總線及控制總線驅動能力的電路。圖中的三態緩沖器如果用74系列TTL芯片,有8位的44、6位的367、4位的125等可供選擇。

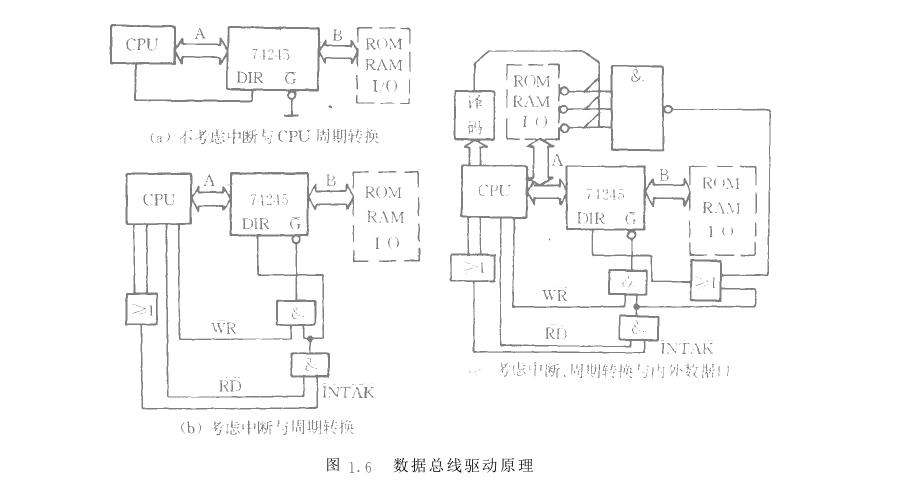

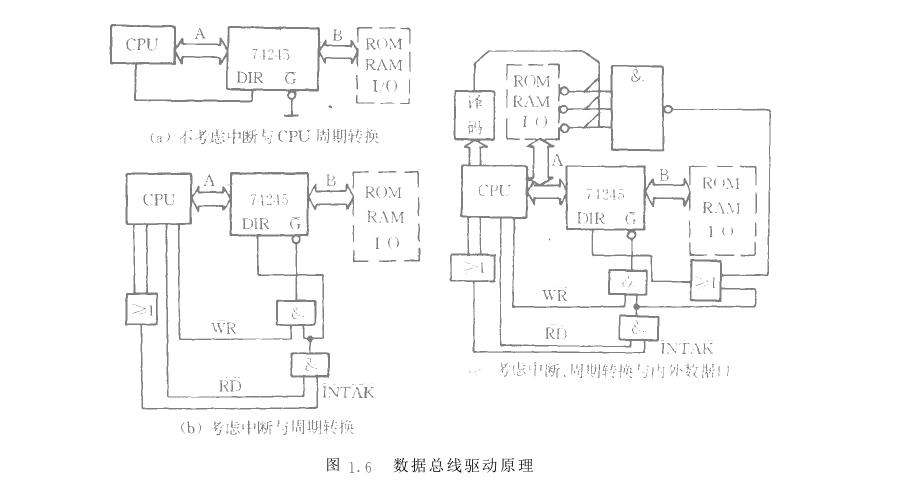

CPU的一些輸入控制線己通過電阻上拉,這樣既能防止因懸空造成的狀態不定,又能增強對一些“線與”的控制線的驅動能力。數據總線是雙向總線,相應的驅動電路的設計要復雜得多。數據總線緩沖器可以使用單向緩沖器背靠背組成,也可以直接使用雙向總線緩沖器。如74245即為常用的8位雙向緩沖器。74245在A、6兩側各有八根一一對應的數據線,另外有一個位能端G和一個方向控制端DIR。其工作方式為:G為邏輯1時PA、U之間斷開:G為邏輯0時名DIR=“0”,則A流向15,反之DIR=“l”時,B流向A。

根據74245的工作方式PF難驗證圖1.6所示的驅動電路能夠保證CPL J對位于?化H另一側的ROM、XAM及I/O芯片執行正確的讀/寫操作。然而這一簡單的數據總線驅動電路存在兩個問題。首先,它不支持來自I心接口的Z奶方式2中斷。這是因為當這種中斷發生時,CPU不是以更D有效P6是以M都IORQ同時有效作出響應的,致使芯片送出的中斷向量無法通過總線緩沖器到達CP耀2g使74245兩側的總

線狀態出現競爭。其次,由于總線緩沖器的使能端(;始終有效,使它處在“非讀即寫”的狀態,從而在讀/寫操作的間隔中,外部器件仍作為負載,加大了總線緩沖器的功耗。改進后的電路如圖1.6(b)所示。一方面,增加了中斷應答信號1N1AK=M1、IoRq,對方向的控制,使數據總線緩沖器在中斷響應周期保持E到A的正確方向;另一方面,使能端G僅在而W更或更而萬滅其中之一有效時把74245接通,從而避免了不必要的功耗。

在圖15(b)中,所有外部數據接口均位于74245的同側,如果CPU與7424;之間另有一部分存儲器或I/O芯片(多板結構的微機系統常常如此),則應當把這些芯片的片選信號與非后經或門控制方向端DIR,如圖1.6(c)所示。這樣當CPU存取這些數據口時,74245的指向始終為A到B表明數據在這些芯片與CFU之間流動。顯然這個電路不完善,它不支持來自這些芯片的向量中斷。

更為復雜的總線驅動邏輯電路完全可以通過以上逐層深入的方法設計出來。必要時可以借助于卡諾圖化簡設計結果。根據微機系統的具體結構,可以使設計的數據總線驅動器支持內、外向量中斷,支持內、外DMA操作,甚至支持多處理器系統。以上設計原理同樣適用于其它類型的CPU或單片機,只是要注意選擇相應的控制信號。(本文來源:正航儀器)

http://www.szzizhi.com